Category: ASIC

-

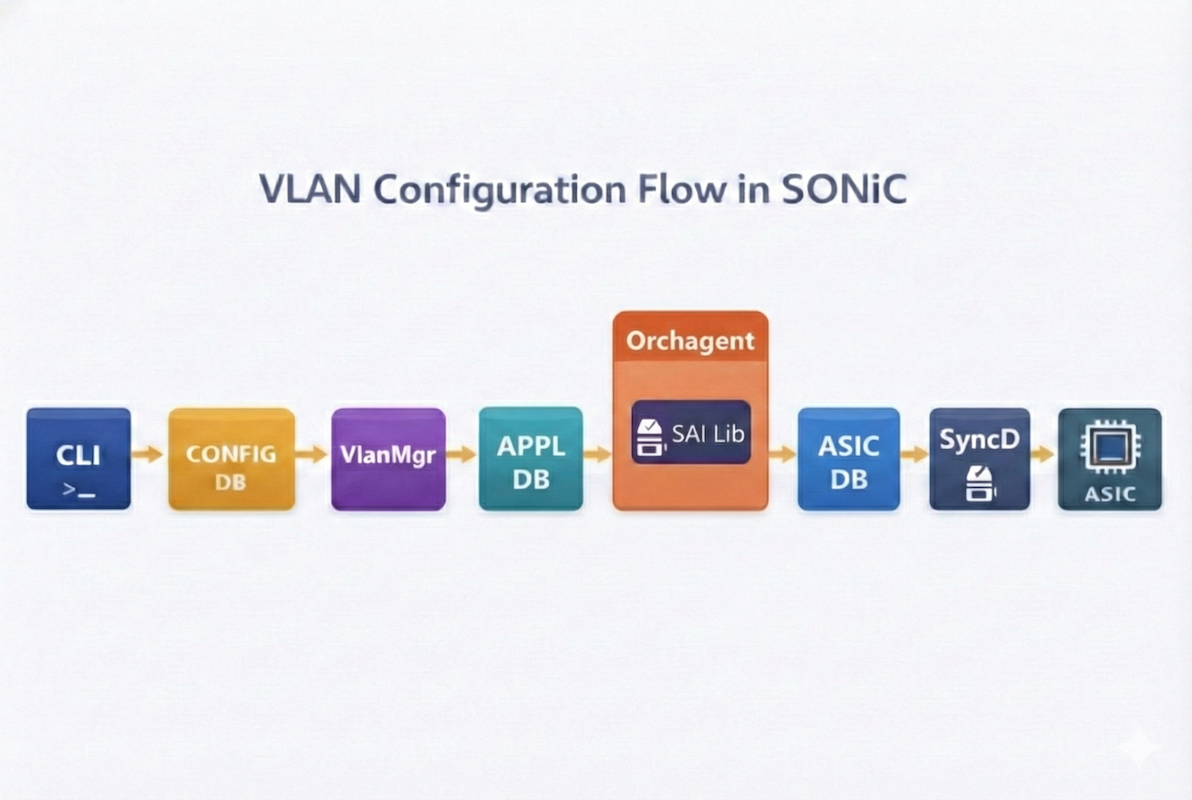

SONiC departs from a traditional networking operating system where configuration commands directly update the hardware tables. Instead, SONiC transforms user intent/configuration to a system state via shared data models and control plane responsibilities spread across loosely tied services. This article examines SONiC from a system design perspective, using VLAN creation as an example to deep…

-

A hyperscaler Ethernet switch isn’t just a big router — it’s a physics experiment. Inside that box, terabits are flying through copper traces every second. The silicon ASICs are tuned to keep GPU clusters fed, and that design philosophy is very different from the enterprise or general-purpose data center switches you’ve seen before. Switch Pipelines:…

-

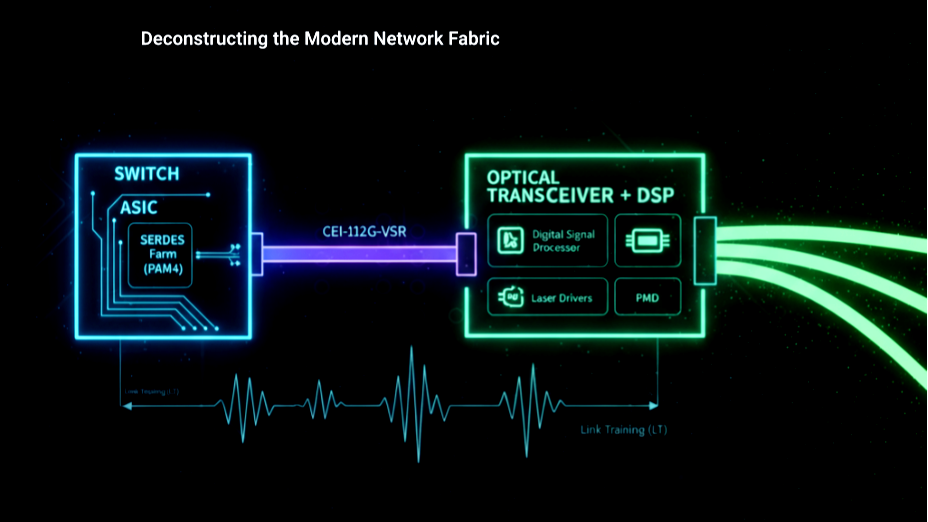

The shift from 1G copper to 400G/800G PAM4 is not a mere incremental upgrade but a complete re-architecture of the network interfaces. For engineering teams building next-gen switches and PHYs the challenge has evolved. It is no longer about optimizing a single PHY chip. Today, it is about orchestrating a distributed electrical-optical system where every…

-

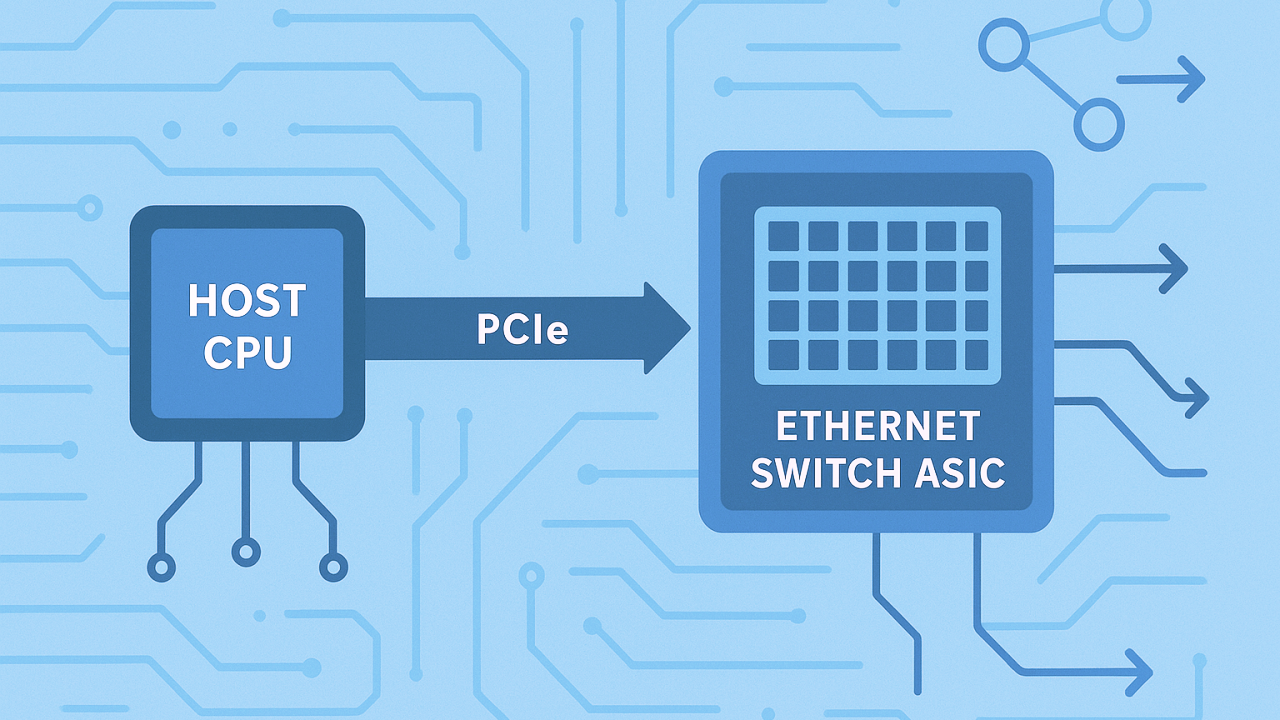

In the world of high-speed networking, the spotlight often shines on the incredible silicon feats: the multi-terabit Ethernet Switch ASICs, the advanced 800G PHY integration, and PAM4 signaling. Yet these capabilities are inert without the software and firmware layers that configure, control, and observe them. Software defines behavior, silicon enforces it. This article delves into…